# 8. CONVERSIONS ANALOGIQUE-NUMÉRIQUE NUMÉRIQUE -ANALOGIQUE

Initiation à l'électronique

JEAN-MICHEL SALLESE

**CONVERSION N/A ET A/N**

**CONVERSION N-A ET RESEAU R-2R**

**CARACTÉRISTIQUES DES CONVERTISSEURS**

**INTERFACES NUMÉRIQUES DES CONVERTISSEURS**

**ECHANTILLONAGE ET CONVERTISSEURS**

## CONVERTISSEUR N/A

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 3

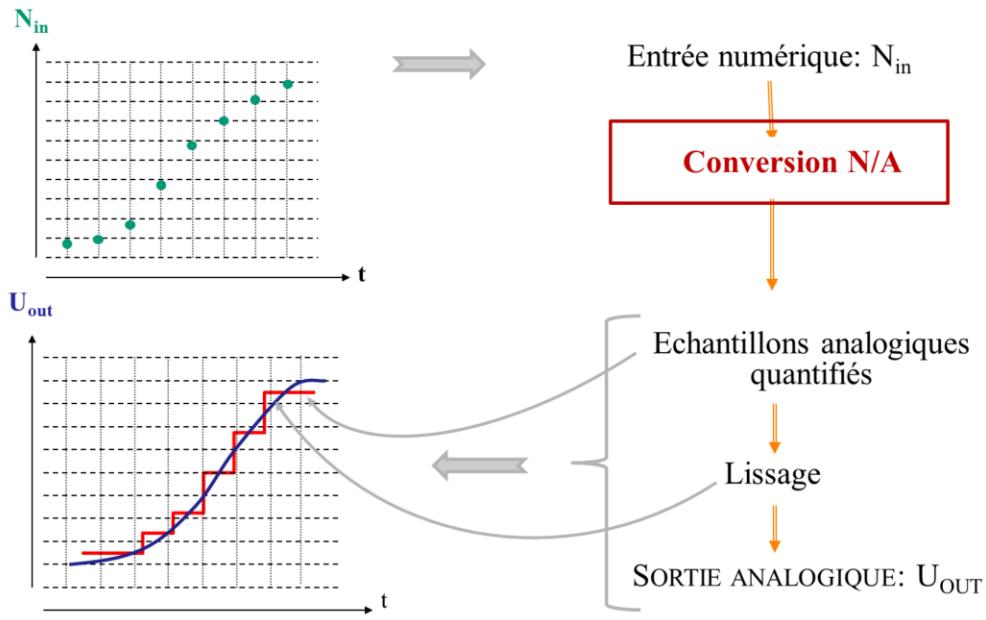

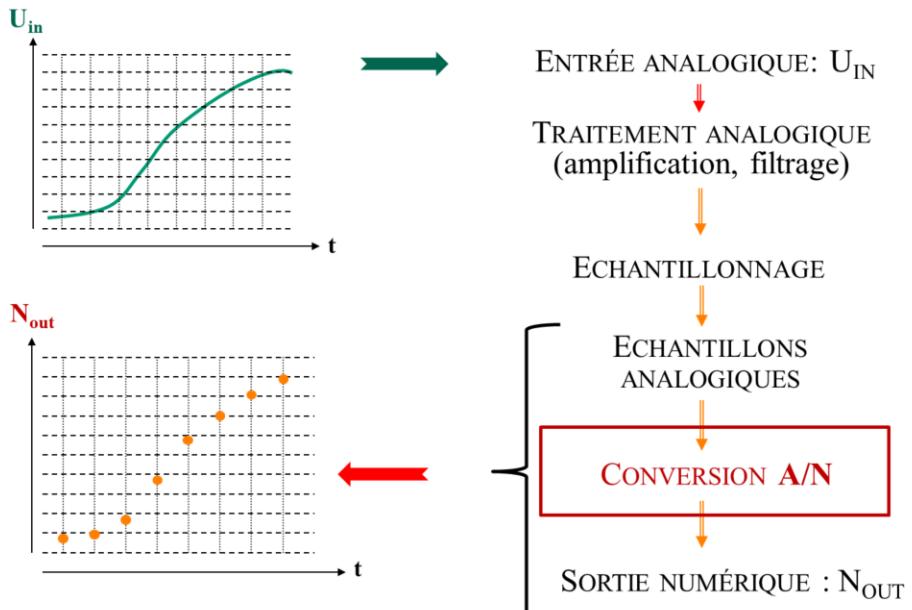

La conversion de données continues analogiques en données discrètes numériques s'effectue à l'aide de convertisseurs analogique/numérique.

La conversion inverse, c'est-à-dire de données numériques vers des données analogiques, requiert des convertisseurs numérique/analogique.

## CONVERTISSEUR N/A UNIPOLAIRE À N BITS

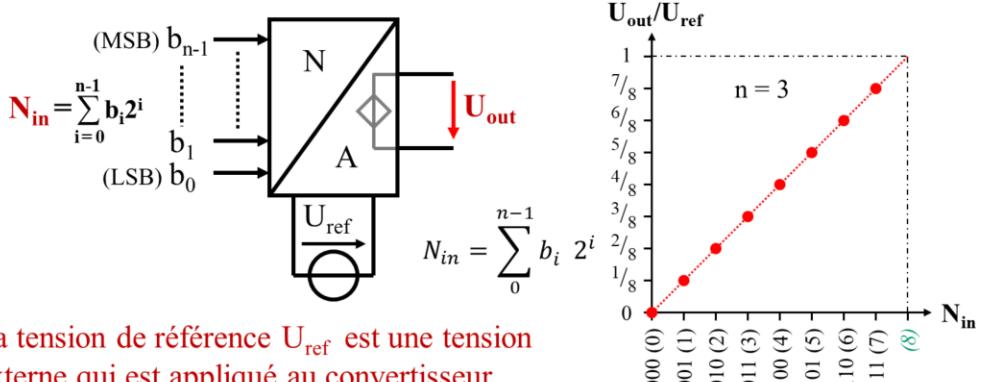

Un convertisseur numérique/analogique transforme un nombre  $N_{in}$  codé sur  $n$  bits en base 2 en une grandeur analogique, généralement une tension  $U_{out}$  (parfois un courant), selon la relation:

$$U_{out} = \frac{U_{ref}}{2^n} N_{in} = \frac{U_{ref}}{2^n} (b_{n-1} 2^{n-1} + \dots + b_1 2^1 + b_0 2^0) \quad b_i = 0 \text{ ou } 1$$

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 4

De nombreux CNA ont une sortie en tension, indépendante de la charge.

D'autres, surtout les CNA rapides, ont une sortie se comportant quasiment comme une source de courant. La tension de sortie est alors directement proportionnelle à la résistance (ou l'impédance) de charge. Cette résistance est souvent intégrée dans le circuit.

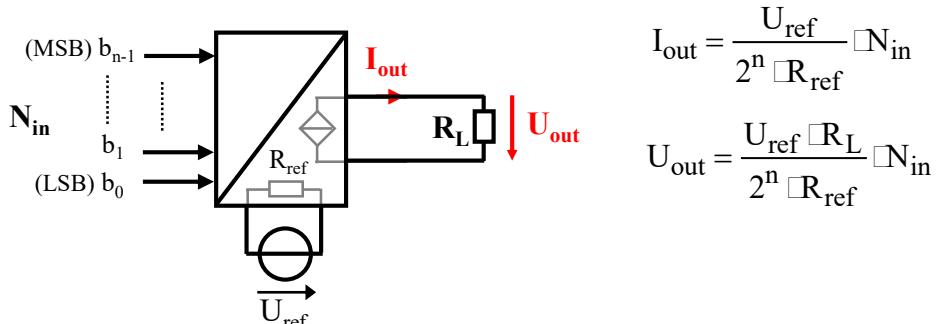

## CONVERTISSEUR N/A BIPOLAIRE A N BITS

$$U_{out} = -U_{ref} + \frac{U_{ref}}{2^{n-1}} N_{in} = -U_{ref} + \frac{U_{ref}}{2^{n-1}} (b_{n-1} 2^{n-1} + \dots + b_1 2^1 + b_0 2^0)$$

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 5

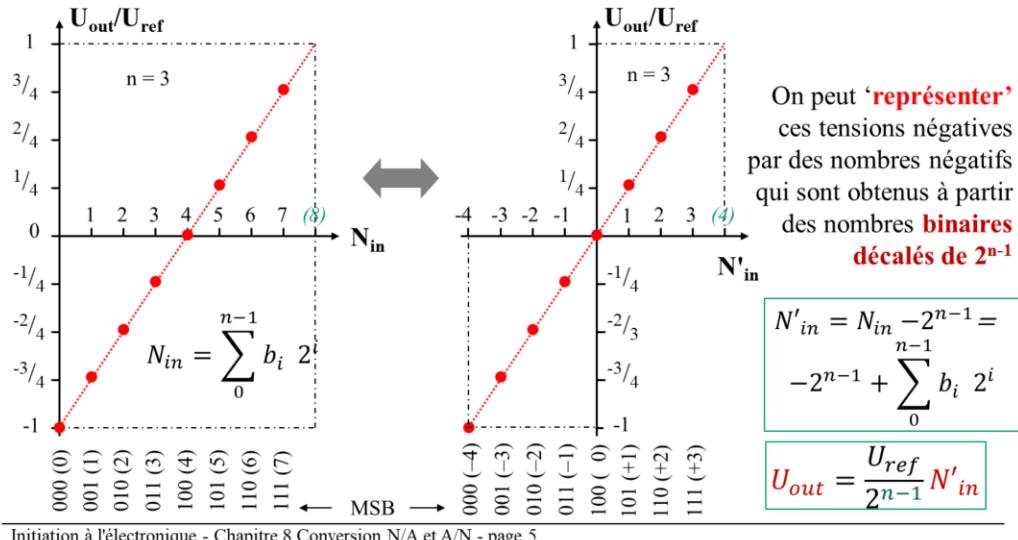

Le code binaire pur représente des entiers positifs:

$$N_{in} = \sum_{i=0}^{n-1} b_i 2^i$$

Le code binaire décalé (offset binary) représente des entiers négatifs et positifs:

$$N'_{in} = N_{in} - 2^{n-1} = -2^{n-1} + \sum_{i=0}^{n-1} b_i 2^i$$

(mais bien entendu les coefficients  $b_i$  sont toujours 0 ou 1, ils ne prennent pas de valeur négative)

Attention, l'entrée est toujours  $N_{in}$ , mais le code binaire décalé permet de 'représenter' des nombres binaires négatifs, par exemple sur le graphique, mais en réalité le circuit n'est 'alimenté' qu'avec des nombres binaires positifs.

## CODES BINAIRE ET BINAIRE-DÉCALÉ

Exemple avec **n = 4**

**binaire**

$N = \sum_0^{n-1} b_i 2^i$

Remarque:

Le nombre qui

sera en entrée est

toujours binaire

|                    |

|--------------------|

| 0 <=> 0000 <=> -8  |

| 1 <=> 0001 <=> -7  |

| 2 <=> 0010 <=> -6  |

| 3 <=> 0011 <=> -5  |

| 4 <=> 0100 <=> -4  |

| 5 <=> 0101 <=> -3  |

| 6 <=> 0110 <=> -2  |

| 7 <=> 0111 <=> -1  |

| 8 <=> 1000 <=> 0   |

| 9 <=> 1001 <=> +1  |

| 10 <=> 1010 <=> +2 |

| 11 <=> 1011 <=> +3 |

| 12 <=> 1100 <=> +4 |

| 13 <=> 1101 <=> +5 |

| 14 <=> 1110 <=> +6 |

| 15 <=> 1111 <=> +7 |

**binaire décalé (offset binary)**

$N' = -2^{n-1} + \sum_0^{n-1} b_i 2^i$

Utile pour la

‘représentation’.

## CONVERTISSEUR A/N

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 7

La conversion de données continues analogiques en données discrètes numériques s'effectue à l'aide de convertisseurs analogique/numérique.

La conversion inverse, c'est-à-dire de données numériques vers des données analogiques, requiert des convertisseurs numérique/analogique.

## CONVERTISSEUR A/N UNIPOLAIRE

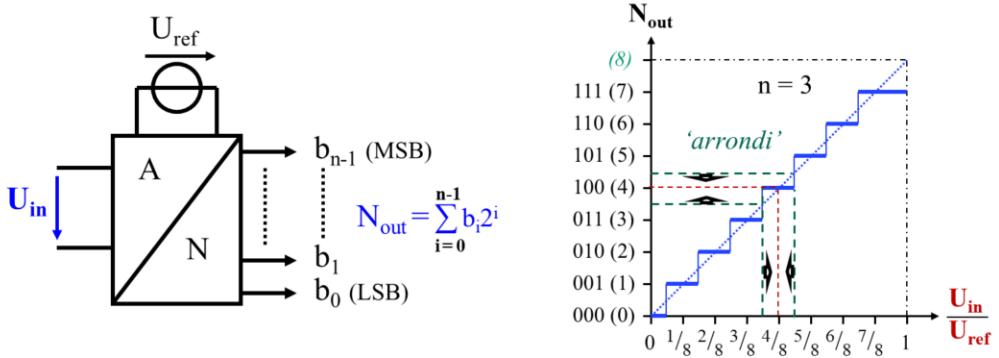

Un convertisseur analogique/numérique transforme une grandeur analogique, le plus souvent une tension, en un nombre codé en binaire sur  $n$  bits suivant la relation:

$$N_{out} = b_{n-1}2^{n-1} + \dots + b_12^1 + b_02^0 = \text{Round}_{base\_2}(2^n \frac{U_{in}}{U_{ref}}) \quad b_i = 0 \text{ ou } 1$$

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 8

Une conversion de ce type

$$N_{out} = b_{n-1}2^{n-1} + \dots + b_12^1 + b_02^0 = \text{entier}(2^n \frac{U_{in}}{U_{ref}})$$

entraîne une erreur systématique de  $U_{ref}/2^{n+1}$ , soit un demi-pas de quantification.

Mais suivant les applications, cette imprécision est négligeable, surtout si le nombre de bits est élevé (16 ou plus).

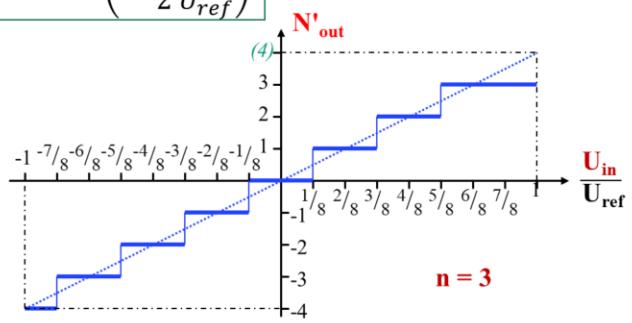

## CONVERTISSEUR A/N BIPOLAIRE

Si la grandeur analogique d'entrée du convertisseur N/A est positive ou négative, la valeur de sortie sera donnée par:

$$N_{out} = Round_{base\_2} \left( 2^n \frac{U_{in} + U_{ref}}{2 U_{ref}} \right) = b_{n-1} 2^{n-1} + \dots + b_1 2^1 + b_0 2^0$$

Mais dans ce cas, le code de sortie est généralement en binaire décalé de  $2^n \frac{U_{ref}}{2 U_{ref}} = 2^{n-1}$

$$N'_{out} = N_{out} - 2^{n-1} = Round_{base\_2} \left( 2^n \frac{U_{in}}{2 U_{ref}} \right)$$

*N'out peut être >0 ou <0*

**N<sub>out</sub>** code

- |     |     |

|-----|-----|

| (7) | 111 |

| (6) | 110 |

| (5) | 101 |

| (4) | 100 |

| (3) | 011 |

| (2) | 010 |

| (1) | 001 |

| (0) | 000 |

## **CONVERSION N-A ET RESEAU R-2R**

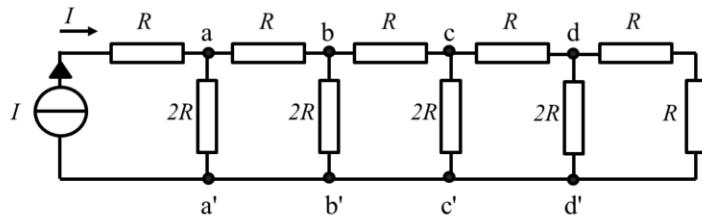

### EXEMPLE DE CONVERSION N-A: LE RÉSEAU R-2R

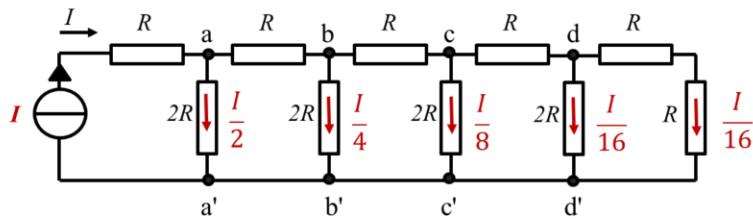

Les courants qui traversent les résistances  $2R$  se trouvent divisés par 2 au fur et à mesure que l'on progresse dans les mailles.

$$I_{dd'} = \frac{I_{cc'}}{2} \quad I_{cc'} = \frac{I_{bb'}}{2} \quad I_{bb'} = \frac{I_{aa'}}{2} \quad I_{aa'} = \frac{I}{2}$$

## EXEMPLE DE CONVERSION N-A : LE RÉSEAU R-2R

### DÉMONSTRATION

## EXEMPLE DE CONVERSION N-A : LE RÉSEAU R-2R

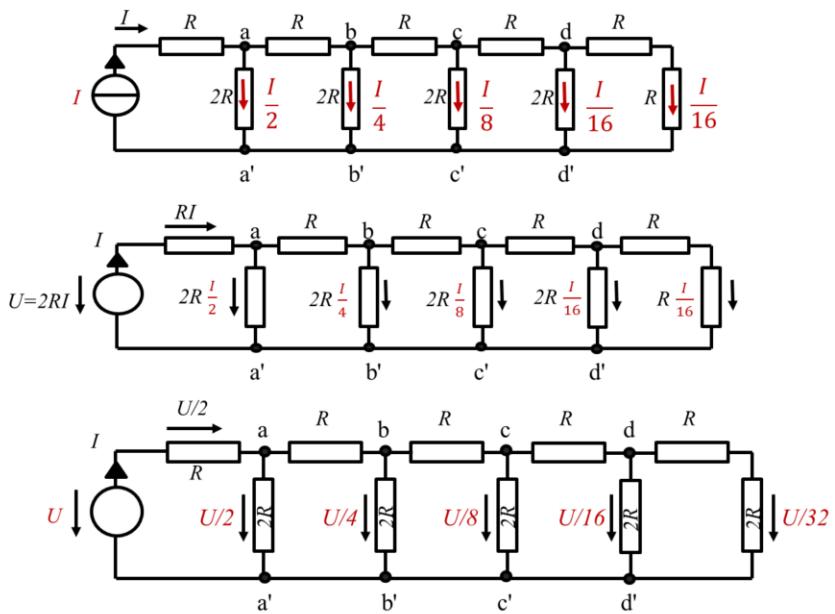

## CONVERSION N-A UNIPOLAIRE A COMMUTATION DE COURANT

$$N_{in} = 1010 \quad \Rightarrow \quad U_{out} = 1 \frac{U}{2} + 0 \frac{U}{4} + 1 \frac{U}{8} + 0 \frac{U}{16}$$

$$U_{out} = \frac{U}{2^4} (1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0)$$

Rappel :  $U_{out} = \frac{U_{ref}}{2^n} N_{in} = \frac{U_{ref}}{2^n} (b_{n-1} 2^{n-1} + \dots + b_1 2^1 + b_0 2^0)$

## CARACTÉRISTIQUES DES CONVERTISSEURS

## CONVERTISSEURS N/A ET A/N, CARACTÉRISTIQUES STATIQUES

### DYNAMIQUE

La **dynamique** est la plage utile de la **grandeur analogique de sortie du CNA**, respectivement d'**entrée du CAN**.

$$\text{CNA unipolaire: } 0 \leq U_{\text{out}} \leq +U_{\text{ref}} \cdot \frac{2^n - 1}{2^n} = \text{FS (Full Scale)} \cong +U_{\text{ref}}$$

$$\text{CNA bipolaire: } -U_{\text{ref}} \leq U_{\text{out}} \leq +U_{\text{ref}} \cdot \frac{2^{n-1} - 1}{2^{n-1}} \cong +U_{\text{ref}}$$

$$\text{CAN unipolaire: } 0 \leq U_{\text{in}} \leq +U_{\text{ref}}$$

$$\text{CAN bipolaire: } -U_{\text{ref}} \leq U_{\text{in}} \leq +U_{\text{ref}}$$

La valeur maximale de sortie d'un CNA unipolaire est souvent appelée la "pleine échelle", "Full Scale" en anglais.

## CONVERTISSEURS N/A ET A/N, CARACTÉRISTIQUES STATIQUES

### Nombre de bits et résolution (ou pas de quantification)

La **résolution** dépend du **nombre de bits n** utilisés pour coder en binaire la grandeur numérique d'**entrée du CNA**, respectivement de **sortie du CAN**.

**La résolution, ou pas de quantification, est le plus petit écart de la valeur analogique** que peut générer un CNA, respectivement que peut distinguer un CAN. Le pas de quantification est parfois appelé (improprement) LSB.

CNA / CAN unipolaire

$$\Delta U_q = \frac{U_{ref}}{2^n}$$

CNA/CAN bipolaire

$$\Delta U_q = \frac{U_{ref}}{2^{n-1}}$$

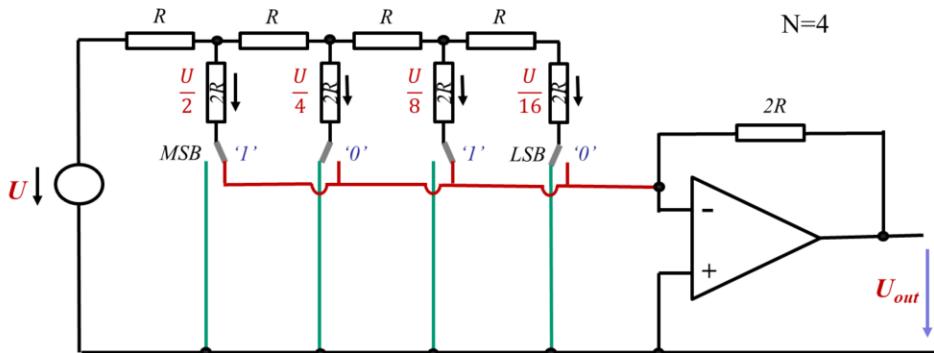

## CARACTÉRISTIQUES TEMPORELLES DES CONVERTISSEURS N/A

### Temps d'établissement N/A (settling time)

Le "settling time"  $t_s$  est le temps que met la sortie du CNA pour atteindre sa **valeur maximale** (Full Scale) avec une erreur relative  $\epsilon$  lorsque l'entrée saute de 0 (tous les bits à 0) à  $N_{\max}$  (tous les bits à 1).

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 18

L'erreur relative par rapport à la valeur maximale, dite "Full Scale" ou "pleine échelle" en français, est généralement donnée en % ou ‰ de la pleine échelle, ou parfois par rapport au pas de quantification.

Cette valeur est importante, car le temps d'établissement est d'autant plus élevé que l'on désire une erreur relative plus réduite, comme on peut le voir sur la figure ci-dessus.

## CARACTÉRISTIQUES TEMPORELLES DES CONVERTISSEURS N/A

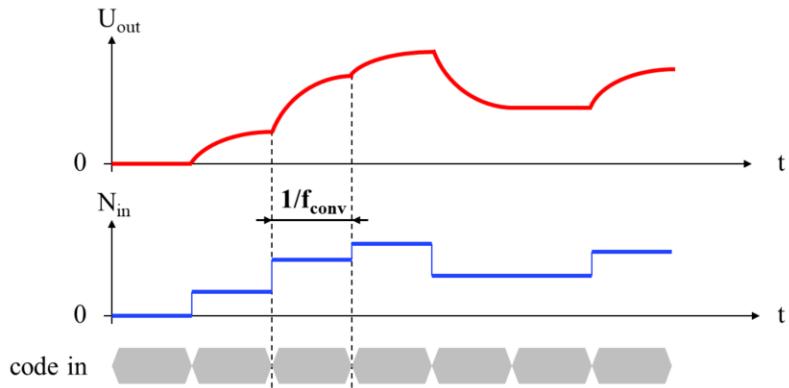

### Fréquence de conversion N/A (conversion rate)

La fréquence de conversion est le **nombre maximum de conversions que le CNA peut effectuer par seconde**. C'est aussi le nombre maximum de nouvelles valeurs d'entrée qu'il peut accepter par seconde (Samples/s).

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 19

On utilise aussi souvent l'expression fréquence d'échantillonnage, Sampling Rate en anglais.

## CARACTÉRISTIQUES TEMPORELLES DES CONVERTISSEURS A/N

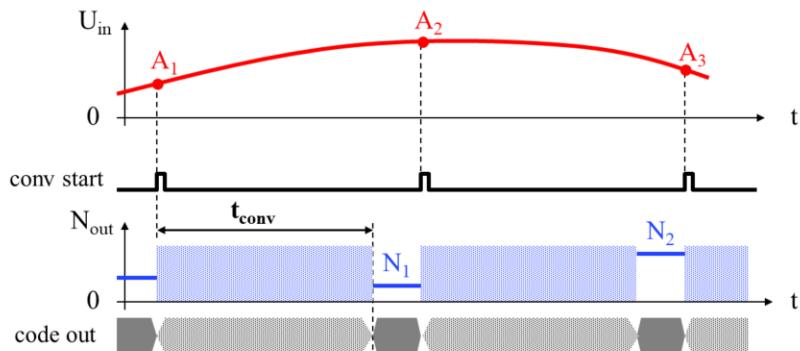

### Temps de conversion A/N $t_{conv}$

Le temps de conversion est le temps nécessaire pour obtenir une valeur numérique (le code binaire) valide à la sortie, à partir de l'ordre de début de conversion.

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 20

La durée de validité des données en sortie dépend de la structure interne du convertisseur. Parfois, comme sur la figure, elles ne sont disponibles que jusqu'au début de la conversion suivante.

Souvent le convertisseur dispose d'un registre de sortie qui conserve le résultat d'une conversion jusqu'à ce que le résultat de la suivante soit disponible.

## CARACTÉRISTIQUES TEMPORELLES DES CONVERTISSEURS A/N

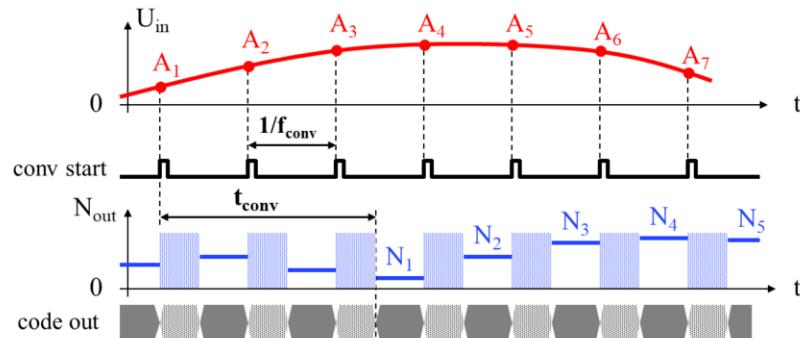

### Fréquence de conversion A/N (conversion rate)

La fréquence de conversion, souvent appelée fréquence d'échantillonnage (Sampling Rate), est le nombre maximum de conversions que le CAN peut effectuer par seconde.

En principe  $f_{\text{conv}} \leq 1/t_{\text{conv}}$ , mais des techniques comme le traitement parallèle permettent de s'affranchir de cette limite.

## INTERFACES NUMÉRIQUES ET CONVERTISSEURS

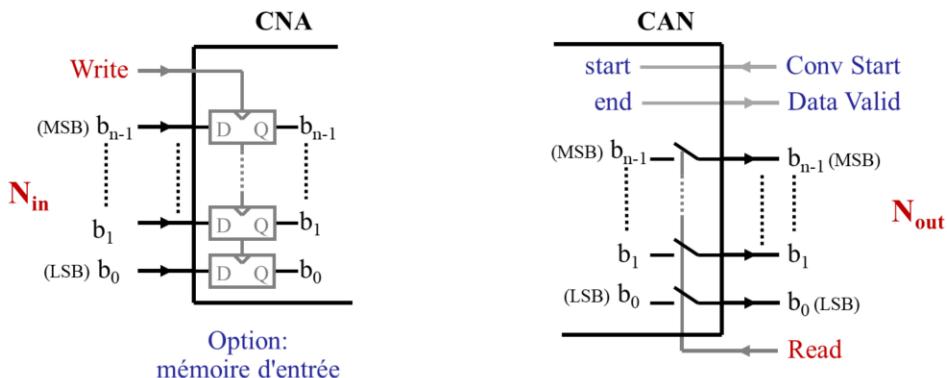

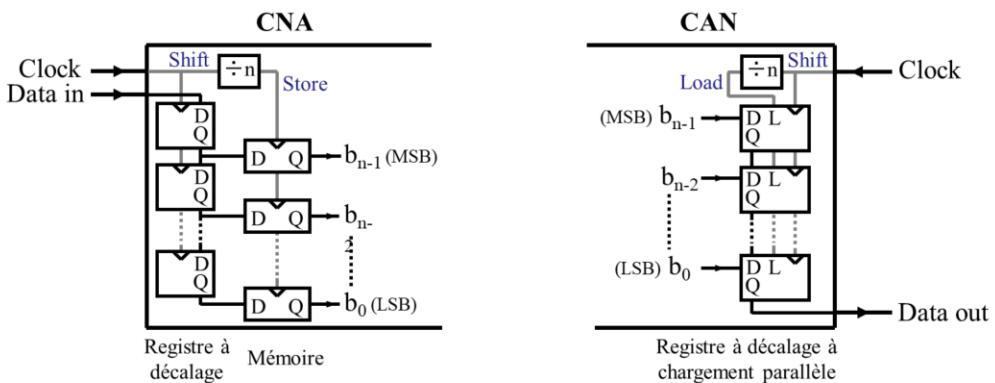

## CONVERTISSEURS N/A ET A/N, INTERFACE NUMÉRIQUE

### INTERFACE PARALLÈLE

Chaque bit a une connexion dédiée. Ils sont **tous écrits dans le CNA ou lus sur le CAN (après conversion digitale) au même instant.**

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 23

Une interface parallèle est facile à gérer et peut atteindre des débits élevés. Dans une interface parallèle, le transfert des data, dans le CNA ou hors du CAN, s'effectue de manière parallèle et en même temps.

Il faut par contre autant de connections que de bits à traiter.

Il peut s'agir d'une limitations selon le câblage.

## CONVERTISSEURS N/A ET A/N, INTERFACE NUMÉRIQUE

### INTERFACE SÉRIE

Les bits sont transmis l'un après l'autre sur une connexion unique.

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 24

Une interface série, si elle est plus compliquée à gérer et plus lente qu'une interface parallèle, a l'avantage d'être plus économique puisqu'elle ne nécessite que trois connexions: Clock, Data et masse.

## CONVERTISSEURS N/A ET A/N, INTERFACE NUMÉRIQUE

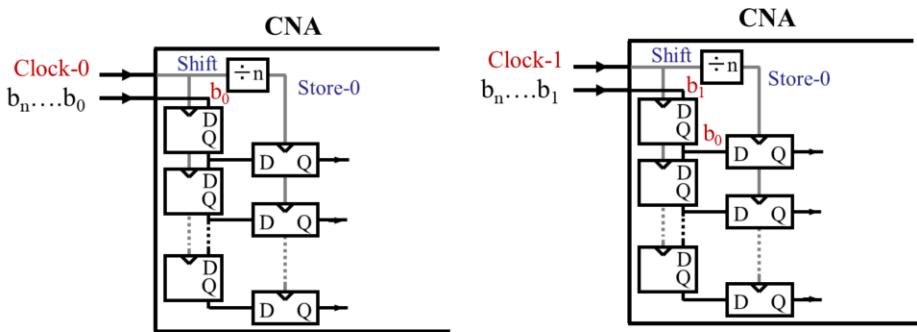

### INTERFACE SÉRIE CNA

Les bits sont transmis l'un après l'autre sur une connexion unique.

Après la première impulsion d'horloge Clock-1:

le bit  $b_0$  ‘avance’ et le bit  $b_1$  ‘prend sa place’

## CONVERTISSEURS N/A ET A/N, INTERFACE NUMÉRIQUE

### INTERFACE SÉRIE CNA

Après la  $n^{\text{ème}}$  impulsion d'horloge Clock- $n$ , le dernier bit  $b_n$  ‘avance’.

En même temps, le diviseur par ‘ $n$ ’ passe à 1 et permet à l’ensemble des  $n$  bits d’être stockés en interne.

Un nouveau paquet de données  $\{b'_i\}$  est prêt à être traité à l’entrée.

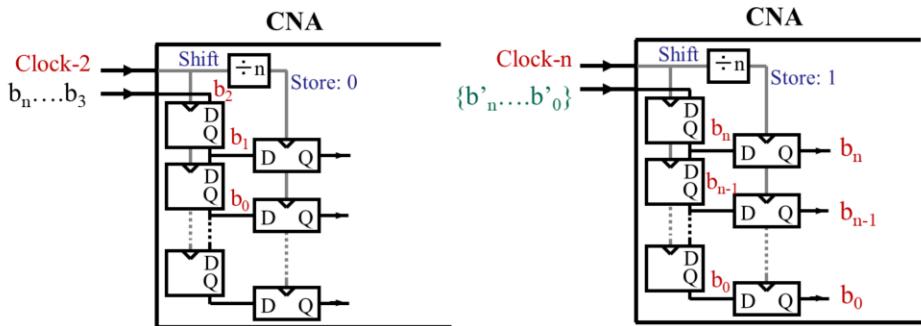

## CONVERTISSEURS N/A ET A/N, INTERFACE NUMÉRIQUE

### INTERFACE SÉRIE CAN

Une fois que les  $n$  bits sont présents sur les entrées D des  $n$  bascules, après un ‘load’ initial au temps Clock-0, ils sont présents sur **D** et sont transmis selon la technique du registre à décalage pour ‘ressortir en série sur une connexion Data Out.

## ECHANTILLONAGE ET CONVERTISSEURS

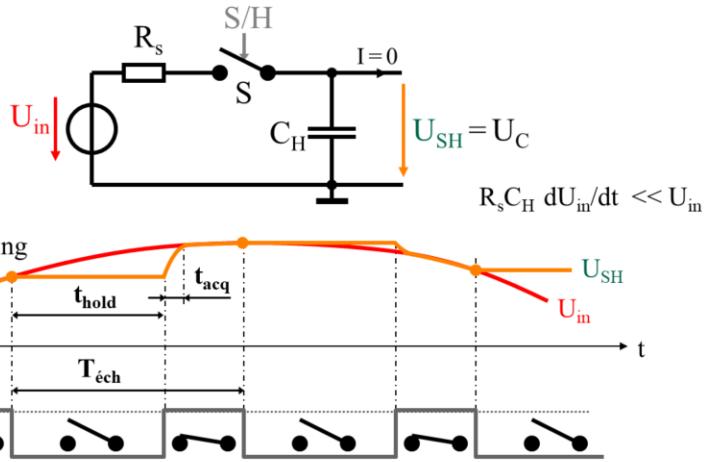

## ECHANTILLONNAGE ET MAINTIEN, PRINCIPE

Un échantillonneur à maintien (Sample and Hold) est un circuit qui prend un échantillon de  $U_{in}$  à un instant précis et conserve cette valeur durant la durée nécessaire à la conversion.

*Sample & Hold*

principe

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 29

Certains CAN ne tolèrent pas que la tension à leur entrée varie durant la conversion, ce qui entraînerait une dégradation de leur précision. La solution à ce problème est d'ajouter devant le CAN un "Sample & Hold", ou échantillonneur à maintien. Souvent ce circuit est intégré avec le CAN.

Un "Sample & Hold" élémentaire et formé d'une capacité et d'un interrupteur.

Lorsque l'interrupteur est fermé, mode tracking :

$$U_C = U_{in} - R_s C_H \frac{dU_C}{dt} \Rightarrow U_C = U_{in} \text{ si } R_s C_H \frac{dU_{in}}{dt} \ll U_{in}$$

Lorsque l'interrupteur est ouvert, mode hold :

$$I_C = 0 \Rightarrow U_C = \text{cst}$$

Dans la pratique, on met souvent un suiveur de tension à la sortie pour éviter que le circuit qui suit ne décharge la capacité, et parfois aussi un suiveur de tension devant l'interrupteur pour supprimer l'influence de  $R_s$  et minimiser le temps d'acquisition. Il existe des circuits intégrés spécialisés qui réalisent au mieux cette fonction.

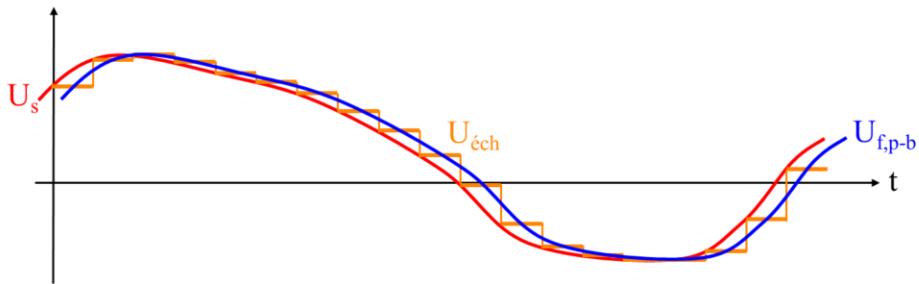

## THÉORÈME D'ÉCHANTILLONNAGE

Pour qu'un signal puisse être reconstruit sans erreur à partir d'échantillons prélevés périodiquement, en passant ceux-ci dans un filtre passe-bas idéal, **la fréquence d'échantillonnage doit être supérieure au double de la fréquence la plus élevée composant le spectre du signal échantilloné.**

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 30

Attention, c'est la composante spectrale la plus élevée du signal qui compte et pas simplement la fréquence dominante ou, dans le cas d'un signal périodique, la fréquence fondamentale.

Conséquences:

- Le signal à échantillonner doit avoir un spectre borné, si nécessaire par un filtre passe-bas, dit de garde, précédant l'échantillonneur.

- Les filtres réels imposent une marge de sécurité. Plus la fréquence d'échantillonnage est élevée, par rapport à la limite théorique, moins les contraintes de filtrage sont sévères.

Dans un système échantillonné à  $f_{\text{éch}}$ , la fréquence limite théorique de  $f_{\text{éch}}/2$  est appelée fréquence de Nyquist.

## THÉORÈME D'ÉCHANTILLONNAGE, CONSÉQUENCES

Le signal à échantillonner doit avoir un spectre borné, si nécessaire par un filtre passe-bas, dit de garde, précédant l'échantillonneur.

Les filtres réels imposent une marge de sécurité. Plus la fréquence d'échantillonnage est élevée, par rapport à la limite théorique, moins les contraintes de filtrage sont sévères.

Dans un système échantillonné à  $f_{\text{éch}}$ , la fréquence limite théorique de  $f_{\text{éch}}/2$  est appelée fréquence de **Nyquist**.

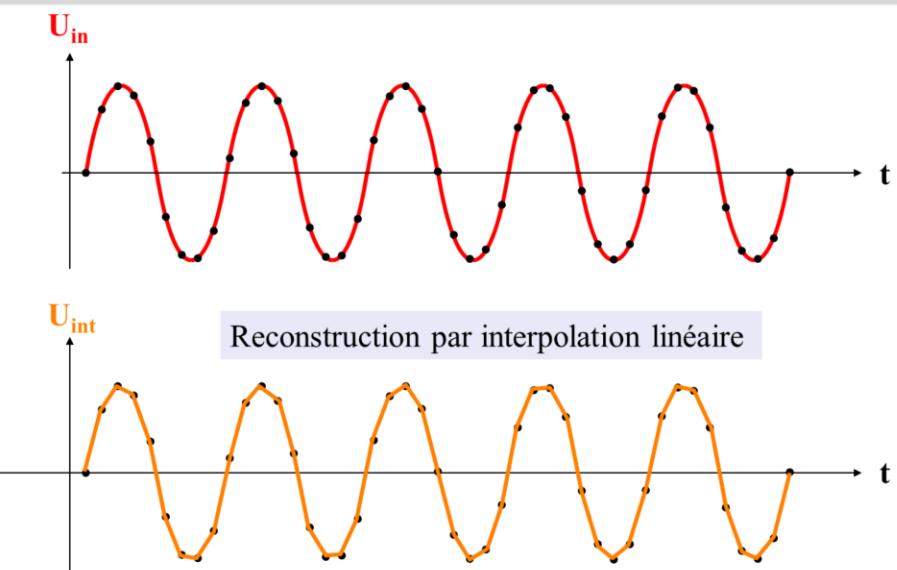

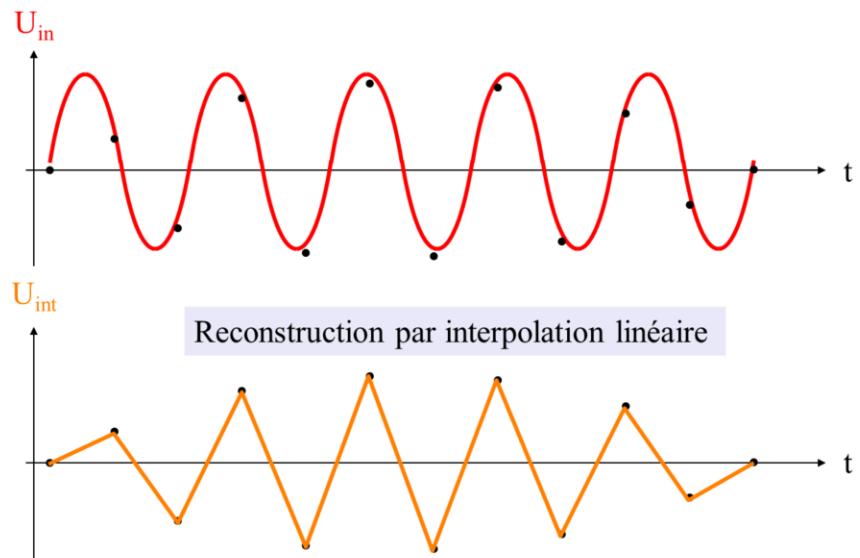

Exemple: échantillonnage d'un sinus à  $f_{\text{éch}} = 8.8 \cdot f_{\text{sinus}}$

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 32

Une interpolation linéaire n'est pas équivalente à un filtrage passe-bas, et ne permet pas une reconstruction parfaite, mais elle est plus simple.

L'échantillonnage à 8.8  $f$  permet de reconstruire assez fidèlement le signal d'origine.

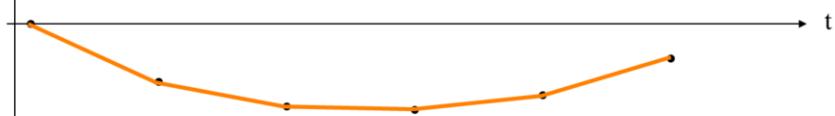

Exemple: échantillonnage d'un sinus à  $f_{éch} = 4.4 \cdot f_{sinus}$

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 33

En divisant encore par 2 la fréquence d'échantillonnage, on retrouve l'aspect temporel et l'allure grossière du sinus.

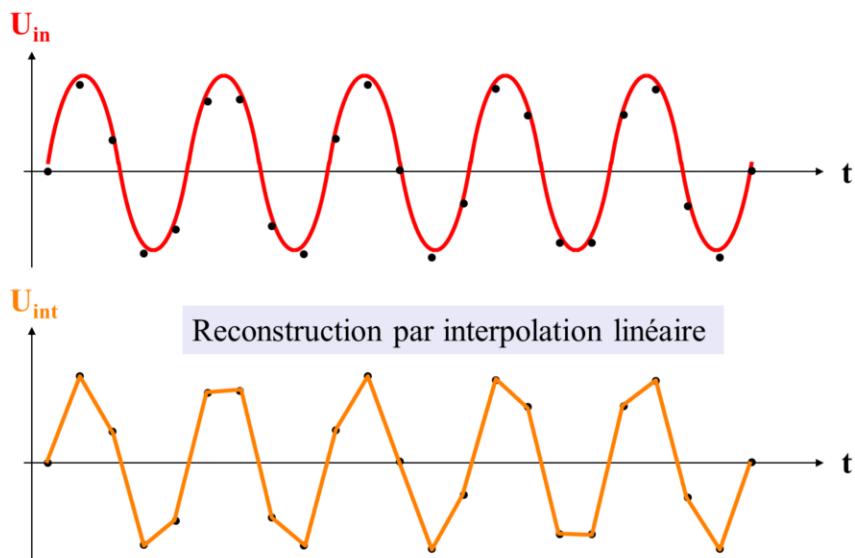

**Exemple: échantillonnage d'un sinus à  $f_{éch} = 2.2 \cdot f_{sinus}$**

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 34

Les variations du signal sont reproduites très grossièrement. On retrouve encore une certaine périodicité mais le détail du signal est perdu.

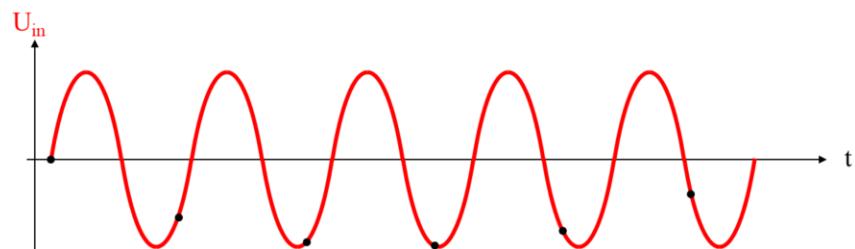

**Exemple: échantillonnage d'un sinus à  $f_{éch} = 1.1 \cdot f_{sinus}$**

**Reconstruction par interpolation linéaire**

**Apparition d'un nouveau signal par sous-échantillonnage**

Initiation à l'électronique - Chapitre 8 Conversion N/A et A/N - page 35

En dessous d'une fréquence d'échantillonnage de  $2f$ , on perd la trace du sinus et le signal reconstruit n'est plus du tout fidèle à l'original.